从A9到骁龙8E6:协处理器演进背后的能效革命

2015年秋天,苹果A9芯片的发布让业界首次见识了协处理器的威力。彼时,移动芯片的性能竞赛还停留在主频和核心数的比拼上,而苹果选择了一条截然不同的道路——用专用硬件解决特定问题。这种设计思路在当时被许多人忽视,如今却成为行业主流。

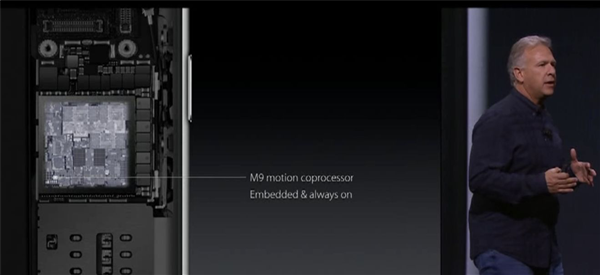

协处理器的技术本质

协处理器的核心价值在于功耗隔离。主处理器需要处理复杂指令,其功耗曲线呈现陡峭特征;而协处理器专为低功耗场景设计,能够在微瓦级别完成任务。当手机需要时刻保持语音唤醒能力时,如果让主处理器持续运行,待机功耗将急剧上升。协处理器的引入则彻底改变了这一局面——它像一位不知疲倦的哨兵,以极低的代价维持着设备的感知能力。

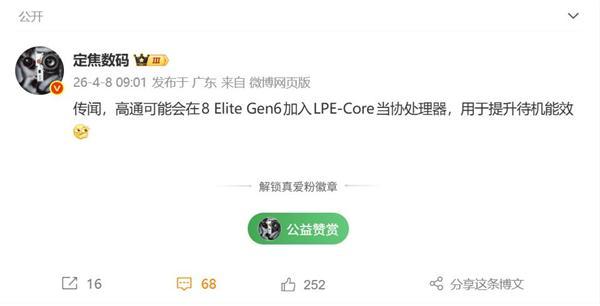

骁龙8E6的LPE-Core架构解析

高通即将在骁龙8E6系列中搭载的LPE-Core协处理器,标志着安卓阵营终于补齐了这块短板。LPE-Core全称LowPowerEngine,是一套完整的低功耗处理子系统。它独立于Kryo主核心运行,拥有专属的电源管理和时钟控制单元。在实际工作中,主处理器可以在大部分时间内保持休眠状态,只有当LPE-Core检测到需要响应的场景时,才会唤醒相应的处理资源。这种设计将待机功耗降低了数个数量级,同时保证了用户体验的连贯性。

2nm工艺的制程红利

骁龙8E6选择台积电2nm工艺并非偶然。更先进的制程节点带来两个关键优势:其一,晶体管密度提升允许在相同面积内集成更多功能单元;其二,漏电流控制显著改善,使得静态功耗大幅下降。对于LPE-Core这样的低功耗模块而言,2nm工艺意味着它可以用更低的电压达到所需的性能目标,同时保持极低的漏电水平。这是硬件层面的能效革命,而非简单的软件优化。

自研架构的战略意义

OryonCPU架构的全面采用代表了高通战略转型的完成。摆脱公版架构束缚后,高通可以根据自身需求定制缓存层次、总线宽度和指令发射单元。2+3+3的核心布局相较上一代2+6方案,本质上是为重负载场景配置了更多中等性能核心。这些核心可以在需要时提供比小核更强的单线程性能,又不会像超大核那样产生巨大的功耗开销。多核协同效率的提升,将在日常应用中转化为更流畅的多任务体验。

面向AI时代的硬件准备

骁龙8E6Pro支持LPDDR6内存是一个被低估的升级。下一代大语言模型对内存带宽的需求远超传统应用,LPDDR6提供的更高频率和更宽总线为此类场景奠定了基础。Adreno850GPU配合协处理器,可以在保持低功耗的同时实现实时AI推理。这意味着未来的旗舰手机将成为真正的个人AI终端,而不仅仅是推送通知的信息接收器。小米18系列作为首发机型,将率先验证这套硬件体系在实际场景中的表现。